Once upon a time in the world of computing, two powerful ideologies emerged—RISC (Reduced Instruction Set Computers) and CISC (Complex Instruction Set Computers). It was a battle of speed vs. complexity, efficiency vs. functionality. But over the years, the lines between them blurred, and today’s processors combine the best of both.

Let’s break down the key differences, advantages, and how this rivalry shaped modern computing. 👇

1️⃣ The Core Philosophy of RISC & CISC

🖥 CISC (Complex Instruction Set Computing)

CISC processors are designed with complex and multi-step instructions that reduce the number of instructions needed in a program.

🔹 Fewer lines of assembly code

🔹 Instructions take multiple cycles to execute

🔹 Optimized for memory efficiency

🔹 Good for general-purpose computing

Think of CISC as English-speaking Peter—someone who speaks fluently using complex vocabulary. He conveys ideas in fewer words, but understanding him takes longer.

🖥 RISC (Reduced Instruction Set Computing)

RISC processors, on the other hand, focus on simplicity and speed by using small, uniform instructions that execute in a single cycle.

🔹 Simple, fixed-size instructions

🔹 1 instruction per cycle (most of the time)

🔹 Optimized for speed and efficiency

🔹 Great for embedded systems and performance-focused applications

RISC is like a beginner learning English—they use basic words and take longer to express ideas, but each step is fast and easy to follow.

2️⃣ The Execution Model: How Instructions Work ⚙️

When you write a high-level program (like in C), the compiler translates it into machine-level instructions that the processor understands. Here’s how the two architectures handle it:

✅ CISC Instructions Example (Multiplication and Addition)

sqlCopyEditMUL R1, R2, 10 ; Multiply R2 by 10 and store in R1

ADD R3, R1, R4 ; Add R1 and R4, store in R3

A single complex instruction does multiple things at once, reducing code size but requiring more processing time.

✅ RISC Instructions Example (Same Multiplication and Addition)

sqlCopyEditLOAD R5, 10 ; Load value 10 into R5

MUL R1, R2, R5 ; Multiply R2 by R5, store in R1

ADD R3, R1, R4 ; Add R1 and R4, store in R3

The same task takes multiple instructions, but each is optimized for speed.

So, CISC reduces the number of instructions but increases execution time per instruction, whereas RISC increases instruction count but executes them faster.

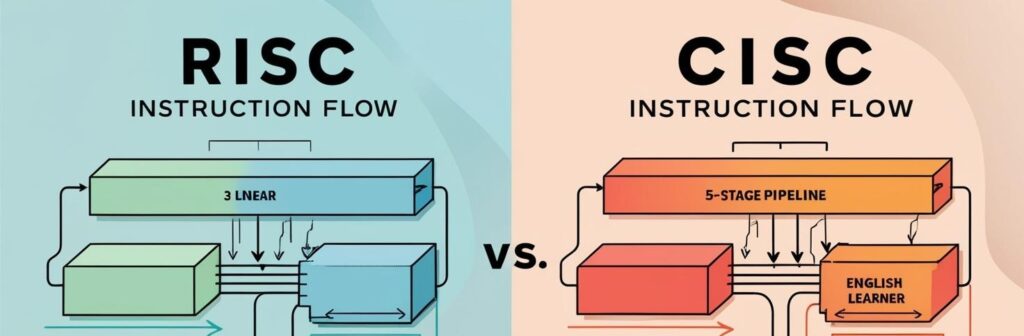

3️⃣ The Role of Pipelining: RISC’s Secret Weapon ⏩

Imagine a restaurant kitchen. If a single chef takes an order, prepares, cooks, and plates each dish before moving on to the next, service is slow. But if different chefs handle each step in parallel, food comes out faster.

That’s pipelining, and RISC processors excel at it.

🔹 Without pipelining (CISC-like approach): Order → Cook → Plate (one order at a time).

🔹 With pipelining (RISC-like approach):

- Order 1: Cook

- Order 2: Prep while Order 1 is cooking

- Order 3: Take order while Order 2 is prepping

Each instruction overlaps with the next, maximizing efficiency.

4️⃣ Load-Store Philosophy: RISC’s Efficiency Boost 🚀

RISC processors follow the Load-Store model, meaning:

🔹 Operations happen in registers, not directly in memory

🔹 Only two operations touch memory: LOAD (read) and STORE (write)

This reduces slow memory access and speeds up execution. However, modern CISC processors use cache memory to minimize this gap.

5️⃣ So, Who Wins? 🏆

🤔 Neither! Modern processors blend both architectures. CISC CPUs use RISC-like pipelines, and RISC chips implement CISC-like optimizations.

✅ RISC excels in embedded systems (low power, small size).

✅ CISC shines in general computing (less memory usage, optimized execution).

The war is over, but the evolution continues. 🚀